Ю.ДАЙЛИДОВ

(EW2AAA),

223610,

г.Слуцк,

пер.Крестьянский,

6,

тел.

5-74-82 (раб.), 2-59-64 (дом).

СИНТЕЗАТОР

ЧАСТОТЫ ДЛЯ ТРАНСИВЕРА С

ПРЕОБРАЗОВАНИЕМ ВВЕРХ

(Продолжение.

Начало в NN1-2/2001)

Нагрузкой

ПС2 служит ФНЧ, формирующий

необходимую АЧХ тракта. Его частота

среза — 41 МГц.

За ФНЧ следуют три каскада усиления, выполненные по одинаковой схеме. Схема усилителей взята из [4]. Эти широкополосные каскады, охваченные отрицательной обратной связью, предназначены для усиления ВЧ. Первые два — усилители напряжения. Третий согласовывает блок преобразователей частоты со входом ТТЛ-микросхем. Он питается напряжением +5 В, и его выход по постоянному току соединен со входом ДПКД.

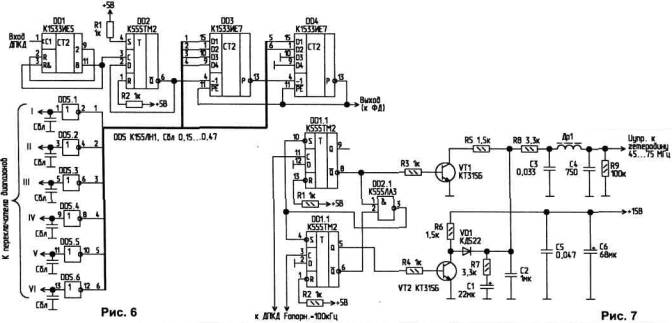

Схема

ДПКД приведена на рис.6. В связи с

тем, что модуль делителя равен 10,

схема реализована на двух

последовательно соединенных

делителях — делителе на 10 (постоянный

коэффициент) и собственно ДПКД,

коэффициент деления которого

изменяется от 11 (для диапазона 0...1

МГц) до 40 (для диапазона 29...30 МГц).

В

первом каскаде делителя на 10

применена быстродействующая микро-

схема

серии 1533, так как входная частота

достигает 40 МГц. Собственно ДПКД

является поглощающим счетчиком с

самозагрузкой данных. Входы данных

развязаны с помощью буферных

элементов-инверторов. Это связано с

тем, что ДПКД и переключатель

диапазонов конструктивно

размещены на разных платах, и длина

жгута достигает 20 см. С выхода ДПКД (вывод

13 DD4) сигнал непосредственно

подается на один из входов фазового

детектора синтезатора.

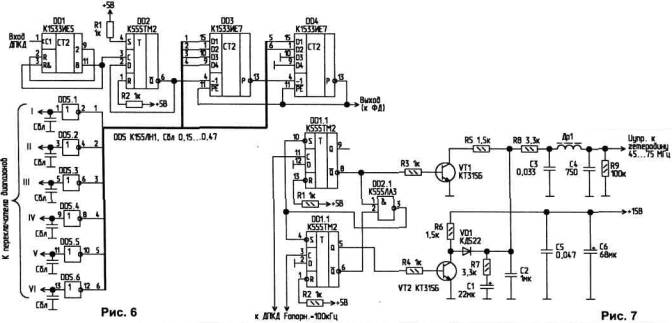

Фазовый

детектор синтезатора (рис.7) — это

хорошо зарекомендовавшая себя

схема на триггерах. Детектор был

доработан — к ФНЧ добавлено еще

одно звено на LC-элементах (Др1 и СЗ).

Это вызвано тем, что если на варика-пе

ГУНа будет присутствовать

напряжение опорной частоты (100 кГц),

трансивер будет принимать (передавать)

сетку частот с шагом 100 кГц, хотя и

значительно ослабленную.

Рис.

9

Питание

на ФД подается от отдельного

стабилизатора в блоке питания

синтезатора (это необходимо для

снижения уровня наводок). Величину

напряжения можно регулировать в

пределах +10...+21 В. При настройке

может выясниться, что напряжение на

вари-капе в гетеродине необходимо

повысить для расширения пределов

перестройки частоты. Резистор R9

служит для облегчения захвата

частоты ФАПЧ, особенно на ВЧ-диапазонах.

Этот ответственный блок

синтезатора можно попробовать

собрать (с целью эксперимента) по

схеме, опубликованной в [2]. Цифровая

шкала (частотомер) измеряет частоту

выходного сигнала синтезатора и

позволяет контролировать

работоспособность и реальную

частоту всего устройства в целом.

Промежуточная

частота, записанная в ПЗУ

процессорного блока, в данном

случае равна 3 МГц. При первом

включении блока он включается на

диапазон 7 МГц, и, в соответствии со

стандартным расположением частот (на

НЧ-диапазонах Ргет выше РСИГН на

величину ПЧ), ГПД генерирует

начальную частоту диапазона 10 МГц.

В связи с тем, что первая ПЧ в

трансивере кратна 500 кГц, начальная

точка настройки устанавливается

точно посередине диапазона.

Например, в диапазоне 0...1 МГц — 500

кГц, в диапазоне 28...29 МГц — 28,5 МГц и

т.п.

В

счетчиках цифровой шкалы записано

предустановленное значение первой

ПЧ. В связи с тем, что Freт всегда выше

Рсигн, это число равно:

1000000-РПЧ=1000000-455000=545000.

Переключатель

диапазонов служит для подачи кода

на ДПКД синтезатора, переключения

поддиапазонов в гетеродине на 45...75

МГц и переключения диапазонных

фильтров в трансивере (приемнике).

Генератор

плавного диапазона, безусловно,

самый важный блок синтезатора,

определяющий стабильность частоты,

поэтому при его конструировании

приняты особые меры. Это

практически еще один функционально

законченный синтезатор частоты,

работающий в диапазоне 10... 11 МГц и

имеющий шаг перестройки 61 Гц. Схема

описана в [5]. Несмотря на

значительно усложнение схемы,

такое решение оправдано сервисными

удобствами (память, расстройка в

широких пределах, сканирование и т.д.).

Разумеется,

можно изготовить и другой ГПД,

учитывая требования, которые к нему

предъявляются — термостабилизация,

жесткая конструкция и т.д. Но что

касается долговременной

стабильности частоты — параметры

такого синтезатора будут ниже.

Вопреки распространенному мнению,

процессорный блок практически не

шумит и не создает "пораженных

точек" при соблюдении простейших

мер электромагнитной

совместимости.

Наладить

подобный ГПД, по мнению автора,

проще, чем добиться хорошей

термостабильности у обычного

генератора.

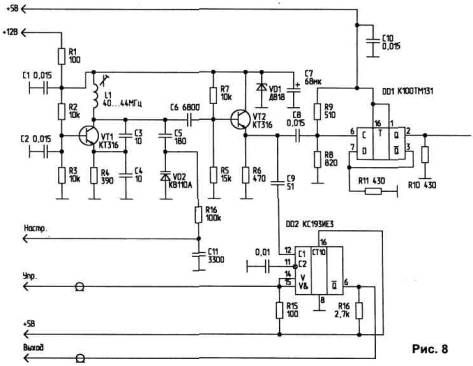

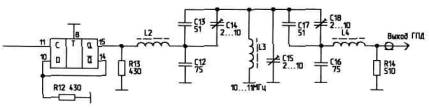

Схема

ГПД из [5] приведена на рис.8.

Доработан только один узел — после

делителя на 4 находится полосовой

фильтр L2...L4, С12...С18, выделяющий

требуемую полосу частот (10...11 МГц) и

формирующий из меандра синусоиду.

Сигнал с полосового фильтра

подается на процессорный смеситель

(ПС1).

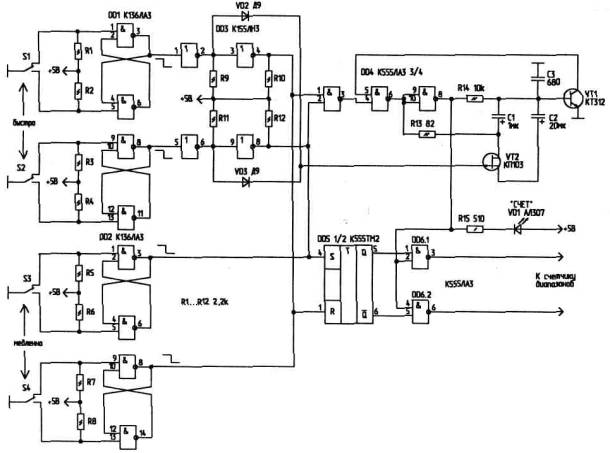

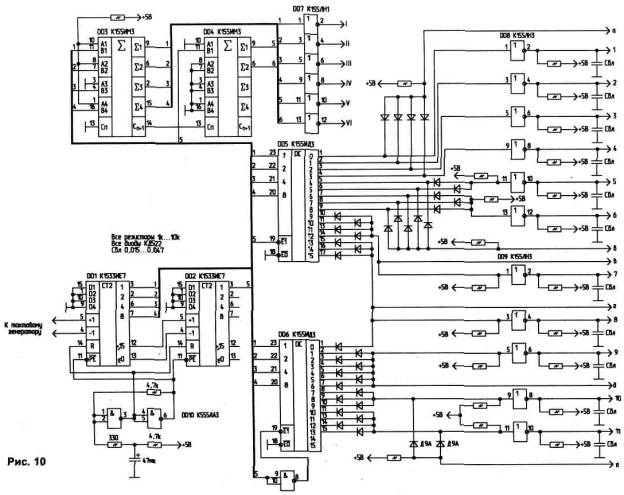

Принципиальные

схемы генератора тактовых

импульсов, счетчика и дешифратора

показаны на рис.9 и 10.

Генератор

тактовых импульсов переключателя

диапазонов выполнен на DD4 и VT1 (рис.9).

Применение

каскада на VT1 позволяет уменьшить

емкость частотозадающих

конденсаторов С1 и С2. Конденсатор

СЗ устраняет паразитное

самовозбуждение на ВЧ во время

включения. Переключатель скорости

счета выполнен на элементах DD3, VD2, VD3,

VT2. При нажатии выбранной кнопки (S1...S4

— "Диапазон вверх/вниз", "медленно/быстро"),

VT2 отпирается низким уровнем с

вывода 2 DD3 через диод VD2 (или с

вывода 6 DD3 через диод VD3), и

параллельно С1 подключается С2.

Частота генератора снижается.

Элементы DD1 и DD2 — защита от "дребезга"

контактов. Переключатель

направления счета — триггер DD5 и

"ворота" (два элемента DD6).

Счетчик

диапазонов выполнен на двух

реверсивных двоичных счетчиках DD1 и

DD2 (рис.10). На DD10 собрана схема сброса

в "О", или (при модернизации)

можно сделать так, чтобы при первом

включении аппарата счет диапазонов

(переключение) начинался не с

первого (0...1 МГц), а, например, с 15 (14...15

МГц). Для этого на входы "R"

микросхем DD1 и DD2 подают логический

"О", а на входы записи данных —

число 15 в двоичном эквиваленте.

Сумматоры

DD3 и DD4 необходимы для того, чтобы

код, подаваемый на ДПКД, начинался

не с 0, а с 11. Шины данных последнего

обозначены на рис.10 римскими

цифрами.

На

входе первого слагаемого

сумматоров постоянно записано

число 11. Следовательно, на выходе

шины данных (буферы-инверторы) DD7 (рис.10)

будет это число плюс содержимое

счетчиков. В данном случае — числа

от 11 до 41.

Два

счетчика типа ИЕ7, конечно,

позволяют считать до 256, и можно

обойтись без сумматоров. Но в этом

случае было бы 10 лишних шагов счета

— от О до 11 (если не делать

предустанов-ку), и, что более важно,

микросхема DD4 использовалась бы

неэффективно (не использовалось бы

более половины выходов). Счет

начинался бы только с 11-го выхода, и

потребовалась бы установка еще

одного дешифратора такого же типа,

для того чтобы иметь 30 выходов (на

каждый диапазон).

Дешифраторы

DD5 и DD6 управляют схемой совпадений

на диодах (ди-одно-транзисторная

логика), сигналы с которой через

соответствующие "шинные

формирователи" DD8 и DD9 подаются на

узлы синтезатора и трансиве-ра.

Сигналы переключения подциапа-зонов

в гетеродине 45...75 МГц обозначены на

рис.10 русскими буквами (от а до е).

Они подаются на соответствующие

ключи в блоке гетеродина.

Остальные цифровые обозначения — это сигналы переключения входных цепей (ДПФ) в приемнике. Шина выходит на системный разъем синтезатора "коммутация ДПФ", расположенный на задней стенке аппарата, и далее, через кабель, в трансивер.

(Продолжение

следует)