СИНТЕЗАТОР ЧАСТОТЫ ДЛЯ ТРАНСИВЕРА С ПРЕОБРАЗОВАНИЕМ ВВЕРХ

Ю.ДАЙЛИДОВ (EW2AAA),

223610, г.Слуцк, пер.Крестьянский,

6, тел. 5-74-82 (раб.), 2-59-64 (дом).

(Продолжение. Начало в NN1...3/2001)

Назначения

выходов переключателя диапазонов

для удобства рассмотрения сведены

в табл.1.

Четыре первых выхода коммутации ДПФ в приемнике объединены с помощью диодов в логическую схему "ИЛИ" и включают ФНЧ с F а=4,5 МГц, который является общим для первых четырех диапазонов.

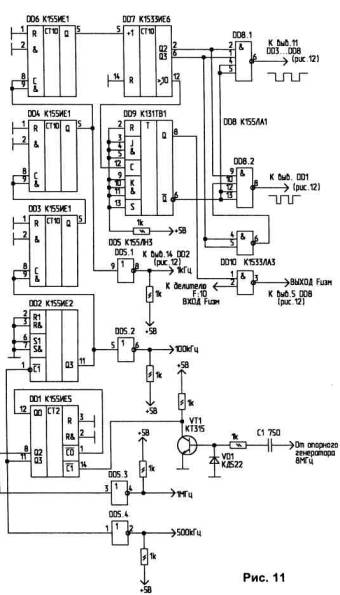

Схема измерительной части частотомера взята из [6] и приведена на рис.11. Она состоит из формирователя калиброванных временных интервалов, счетчиков DD1...DD4, DD6, DD7, триггера DD9, "ворот" DD10, формирователей импульсов записи предустановки счетчиков (запись ПЧ). Из цепочки делителей легко взять необходимые опорные частоты для схемы ФАПЧ, что и сделано в данной конструкции. Частота 1 МГц для работы ФАПЧ и процессорного блока ГПД снимается с вывода 8 DD1 и равна 1 МГц. Частота 500 кГц для схемы ФАПЧ опорного генератора 45 МГц снимается с вывода 11 DD1, частота 100 кГц для ФД синтезатора — с вывода 11 DD2. Частота 1 кГц, снимаемая с вывода 5 DD4, используется в блоке динамической индикации частотомера как тактовая (переключение разрядов).

Все опорные частоты подаются на свои блоки через буферы-инверторы DD5.

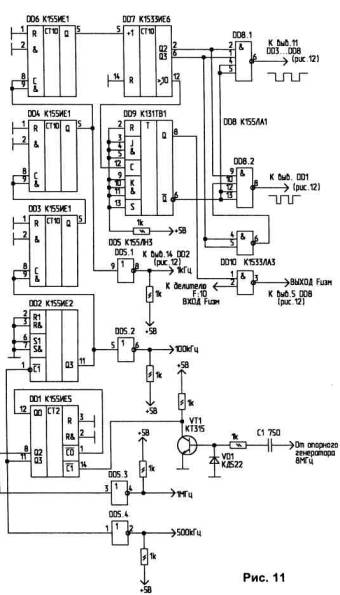

Вход измерительного блока — вывод 2 DD10. На него подается частота гетеродина 45...75 МГц через промежуточный ВЧ-делитель на десять (рис.12). Схема его взята из [7]. Он многократно применялся автором этих строк в различных конструкциях и хорошо зарекомендовал себя. Добавлен простейший преобразователь уровней ЭСЛ к ТТЛ — каскад на транзисторе VT1.

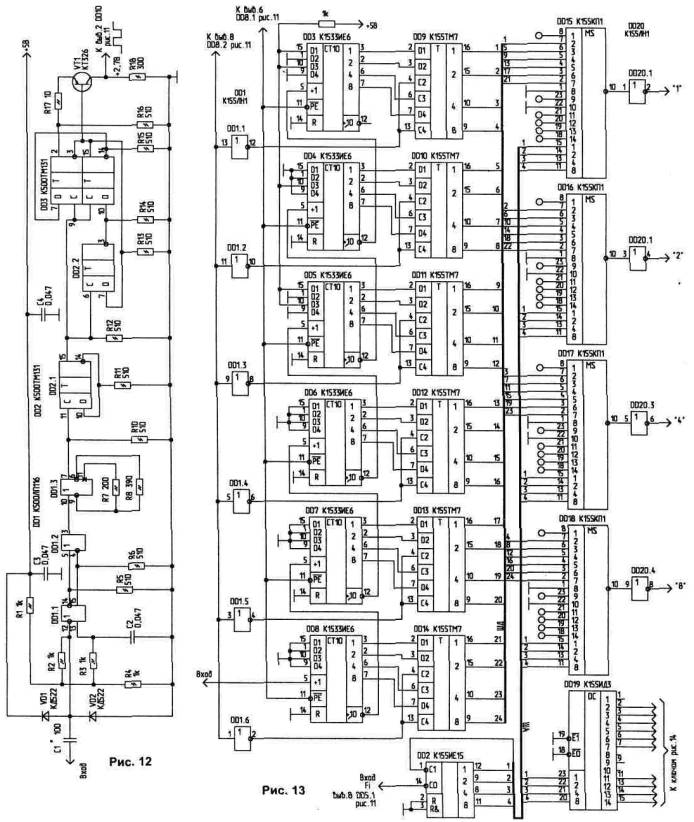

Алгоритм работы блока динамической индикации (рис.13) основан на принципе поразрядного опроса и последовательном включении разрядов индикаторов. Его схема состоит из цепочки десятичных счетчиков DD3...DD8. Функционально они относятся к измерительному блоку цифровой шкалы (рис.11), но конструктивно (на печатной плате) размещены именно в этом блоке. Сигналы со счетчиков подаются на узел промежуточной памяти DD9...DD14. Она нужна для устранения мигания цифр во время счета импульсов. Далее каждый разряд двоичного кода с соответствующих триггеров через свой коммутатор-мультиплексор подается на один общий дешифратор цифр (рис.14). Например, DD15 "собирает" все "1", DD16 — "2" и т.д. в коде 1-2-4-8. К шине адреса (ША, рис.13) коммутаторов параллельно подключена шина адреса дешифратора DD19, который подключает сетки лампы-индикатора к источнику питания +35 В.

Процесс происходит синхронно — коммутаторы собирают код цифр с декады, а детекторы подают соответствующие уровни на выводы индикаторных ламп. В связи с тем, что коммутаторы инвертируют код, на их выходах стоят инверторы DD20.

На схеме блока кружками обозначены входы, не подключенные к коммутаторам DD15...DD18. Выводы 8 и 23 последних с соответствующим кодом 1-2-4-8 можно подключить к процессорному блоку ГПД (шина I на схеме в [5]). Первый служебный разряд лампы цифровой шкалы будет показывать включение "расстройки" трансивера, а девятый номер ячейки памяти (соответствующие ключи на VT1 и VT8 на рис.14) подключаются к выходам дешифратора 8 и О (выводы 10 и 1 DD1 блока A3 в [5]). Конкретное размещение значащих цифр цифровой шкалы приведено на рис.15.

Входы коммутаторов 1 и 22 (рис. 13) заземлены — разряды погашены и не используются. Входы 21, 20, 19, 18 — резервные. Их можно использовать для дальнейшей модернизации блока индикатора, например, для подключения к счетчикам часов или цифрового S-метра трансивера.

Табл. 1

№ диапазона |

Частота настройки приёмника, МГц |

Коммутация гетеродинов «грубо» |

К дел. ДПКД |

F гет. |

Fн ДПФ приёмника, МГц |

1 |

0...1 |

А |

11 |

45,5...46,5 |

0...4 МГц |

2 |

1...2 |

А |

12 |

46,5...47,5 |

|

3 |

2...3 |

А |

13 |

47,5. ..48,5 |

|

4 |

3...4 |

А |

14 |

48,5...49,5 |

|

5 |

4...5 |

Б |

15 |

49,5...50,5 |

4. ..6 МГц |

6 |

5...6 |

Б |

16 |

50,5...51,5 |

|

7 |

6...7 |

Б |

17 |

51,5...52,5 |

6...Э МГц |

8 |

7...8 |

Б |

18 |

52,5...53,5 |

|

9 |

8...8 |

Б |

19 |

53,5...54,5 |

|

10 |

9...10 |

В |

20 |

54,5...55,5 |

9...13МГЦ |

11 |

10...11 |

В |

21 |

55,5...56,5 |

|

12 |

11...12 |

В |

22 |

56,5...57,5 |

|

13 |

12...13 |

В |

23 |

57,5...58,5 |

|

14 |

13...14 |

Г |

24 |

58,5...59,5 |

13. ..17 МГц |

15 |

14...15 |

Г |

25 |

59,5...60,5 |

|

16 |

15...16 |

Г |

26 |

60,5...61,5 |

|

17 |

16...17 |

Г |

27 |

61,5...62,5 |

|

18 |

17...18 |

Д |

28 |

62,5...63,5 |

17...23МГЦ |

19 |

18...19 |

Д |

29 |

63,5...64,5 |

|

20 |

19...20 |

Д |

30 |

64,5...65,5 |

|

21 |

20...21 |

Д |

31 |

65,5...66,5 |

|

22 |

21. ..22 |

Д |

32 |

66,5...67,5 |

|

23 |

22...23 |

Д |

33 |

67,5...68,5 |

|

24 |

23...24 |

Е |

34 |

68,5...69,5 |

23...26 МГц |

25 |

24...25 |

Е |

35 |

69,6...70,5 |

|

26 |

25...26 |

Е |

36 |

70,5...71,5 |

|

27 |

26...27 |

Е |

37 |

71,5...72,5 |

26...30 МГц |

28 |

27...25 |

Е |

38 |

72,5...73,5 |

|

29 |

28...29 |

Е |

39 |

73,5...74,5 |

|

30 |

29...30 |

Е |

40 |

74,5...75,5 |

|

Счетчик разрядов — двоичный счетчик DD2. На его вход подается тактовая частота 1000 Гц с блока формирования опорных частот (вывод 8 DD5.1, рис.11). Вообще, частоту переключения разрядов лампы лучше выбирать ниже, так как чем выше частота, тем ниже яркость свечения. В то же время, желательно не допускать мигания цифр.

Для повышения яркости свечения цифр напряжение питания сеток и катодов лампы ИВ-27м повышено до 35 В.

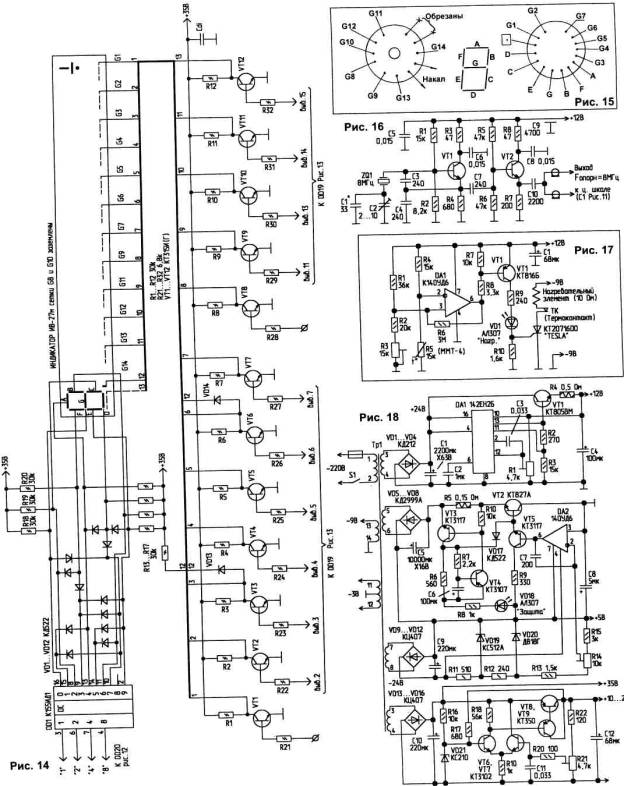

Схема дешифратора цифр блока динамической индикации приведена на рис.14. Ввиду меньшей дефицитности и стоимости, в ней использована микросхема К155ИД1, а не К514ИД2, которая позволяет повысить напряжение на электродах лампы. Микросхема управляет диодным коммутатором VD1...VD12.

При индикации нужной цифры соответствующие ключи в микросхеме открываются, и через диоды снимают напряжение питания с неиспользуемых сегментов-анодов.

Схемы такого дешифратора-преобразователя кода 1-2-4-8 в семисегментный код цифровых индикаторов неоднократно публиковались в радиолюбительской литературе, например, в [9].

Индикация запятых, необходимых после соответствующих разрядов, обеспечивается подачей напряжения на сетки через диоды VD13 и VD14.

Ключи,

управляемые от дешифратора DD19(pnc.13)

и включающие разряды выполнены на VT2...VT7,

VT9...VT12. Они подключаются к выходам

дешифратора со второго (вывод 2) по

седьмой (вывод 7) и с одиннадцатого (вывод

11) по четырнадцатый (вывод 14) DD19.

Выходы 8 и 10 последнего не

используются — разряды погашены (сетки

лампы заземлены). Как уже

отмечалось выше, ключи первого (служебного)

и девятого разрядов работают от

другого дешифратора.

На блок динамической индикации также подаются необходимые сигналы с контроллера (рис.11). Это команда записи в счетчики (предустановка) и в промежуточную память (рис.13).

Вход блока — вывод 5 DD8. На него подается измеряемая частота (предварительно поделенная на 10) через ключ на DD10 (рис.11).

Здесь (рис.

13) DD8—это счетчик сотен герц, DD7 —

единиц килогерц, DD6 — десятков

килогерц, DD5 — сотен килогерц, DD4 —

единиц мегагерц, DD3 — десятков

мегагерц. В счетчики через входы

данных (выводы 15, 1, 10 и 9)

записывается число 54500.

Опорный кварцевый генератор (рис.16) полностью определяет стабильность частоты синтезатора, т.к. от него формируются все опорные частоты схем ФАПЧ и временной интервал измерения частоты в цифровой шкале.

Он вырабатывает частоту 8 000 кГц и собран на VT1 по схеме емкостной трехточки. Точная установка частоты осуществляется подстройкой конденсаторов С1 и С2. ОКГ нагружен на эмиттерный повторитель VT2. Сигнал с него подается на разъем синтезатора "Опорн. 8 МГц" и на блок формирования опорных частот (С1 на рис.11). Для достижения высоких долговременных частотных параметров он помещен в термостат, схема которого приведена на рис.17. Термостат применен от радиоприемника "Волна". Он имеет малые габариты и в данной конструкции питается переменным напряжением 9 В. Небольшая переделка заключается в том, что снимается один (всего их два) термодатчик, и на его место устанавливается термистор (R5). Естественно, для любительских целей термостат можно и не устанавливать.

Блок питания (БП) обеспечивает синтезатор необходимыми для работы узлов напряжениями: +12 В — питание ВЧ-генераторов; +5 В — питание процессорного блока ГПД, питание цифровой шкалы и остальных блоков, собранных на микросхемах; +15 В — регулируемое в пределах +10...21 В напряжение для питания схемы настройки (фазового детектора) гетеродина 45...75 МГц; +35 В — питание лампы индикатора ЦШ; переменное 9 В — питание нагревательного элемен-та термостата; 3,5 В — питание накала лампы индикатора. Схема БП приведена на рис.17. Он состоит из силового трансформатора, выпрямителей и стабилизаторов напряжений.

Стабилизатор +12 В собран по стандартной схеме с применением микросхемы К142ЕН2. Она обеспечивает надежную работу, малые габариты и защиту по току.

Схема стабилизатора +5 В несколько усложнена. Это связано с тем, что цепи, которые он питает, потребляют значительный ток (до 1,4 А) (с процессорным блоком ГПД — до 2 А). Удобна эта схема тем, что регулирующий транзистор можно крепить на радиатор без изолирующей прокладки, т.к. его коллектор соединяется с корпусом.

Стабилизатор опорного напряжения для источника +5 В питается от отдельной обмотки силового трансформатора. Конкретно схема стабилизатора +5 В взята из БП бытового компьютера "Сантака-002". При налаживании следует учитывать, что уровень пульсаций с частотой 50 Гц зависит от точки подключения выходной шины +5 В к стабилизатору. Лучший результат получается, если брать это напряжение прямо с плюсового вывода конденсатора С5, что уточняется при налаживании.

Стабилизатор напряжения настройки гетеродина — слаботочный, он собран на транзисторах VT6...VT9. Резистор R21 обеспечивает регулировку выходного напряжения. От выпрямителя этого стабилизатора питается лампа индикатора цифровой шкалы. Накал лампы индикатора цифровой шкалы питается переменным напряжением, снимаемым с обмотки 11-12 силового трансформатора. Обмотка имеет отвод от середины, который, естественно, заземляется, отрицательное напряжение подается на катод.

С обмотки 13-14 снимается переменное напряжение 9 В для питания нагревательного элемента термостата.

Конструкция и детали

Синтезатор предназначен для использования в составе приемника или трансивера, поэтому, с целью уменьшения и полного подавления различных паразитных наводок и связей, он выполнен в виде отдельного, функционально законченного блока с автономным блоком питания. Шасси-корпус изготовлено из алюминиевого проката и пластин. Его размеры — 230x290x100 мм. На расстоянии 30 мм от передней панели находится вертикальная перегородка размерами 230x100 мм. В этом отсеке помещаются блок динамической индикации цифровой шкалы, платы клавиатуры процессорного модуля ГПД и механизм валкодера с оптопарами.

На расстоянии 70 мм от задней панели расположена еще одна вертикальная перегородка размером 230x100 мм. В этом образовавшемся отсеке размещаются блок питания синтезатора и термостат. Оставшаяся часть шасси-корпуса делится на две равные части горизонтальной перегородкой 230x170 мм, которая опирается на дюралевые бруски, стягивающие корпус. В верхней части отсека вплотную к перегородке расположен гетеродин 45...75 МГц. Он находится в экранирующей алюминиевой коробке размерами 205x85x37 мм.

На небольшом расстоянии от отсека питания на горизонтальной панели симметрично расположены два блока—ОГ и ГПД. Для их крепления в горизонтальной панели вырезаны отверстия по размерам плат, но с таким расчетом, чтобы они опирались на панель краем с оставленной металлизацией со стороны деталей. Узлы закрыты с обеих сторон дюралевыми листовыми экранами (от заводской аппаратуры).

(Окончание следует)