Ю.ДАЙЛИДОВ

(EW2AAA),

223610,

г.Слуцк,

пер.Крестьянский,

6.

тел.

5-74-82 (раб.), 2-59-64 (дом).

СИНТЕЗАТОР

ЧАСТОТЫ ДЛЯ ТРАНСИВЕРА С

ПРЕОБРАЗОВАНИЕМ ВВЕРХ

(Продолжение.

Начало в N1/2001)

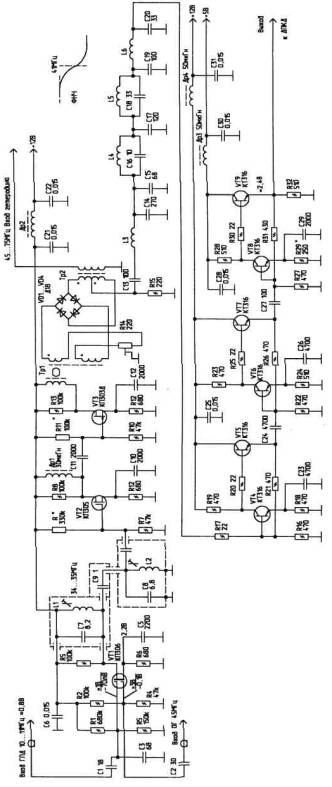

Гетеродин

(рис.4) собран на транзисторе VT1.

Сигнал с него подается на два ис-токовых

повторителя (VT2, VT3). С транзистора VT2

сигнал частотой 45 МГц снимается на

процессорный смеситель ПС1, с VT3

сигнал подается на схему

формирования импульсов (для работы

цифровой части). Схема собрана на

транзисторах VT4 и VT5. В широко

известных схемах согласования

генератора и цифрового счетчика на

микросхемах обычно используется

только один усилитель. Здесь же

усилитель VT4 работает на счетчик DD3

через эмиттерный повторитель, что

повышает верхнюю рабочую частоту

устройства.

С

этой же целью применен и каскад на VT6,

который используется, если

проводник, соединяющий вывод 13 DD3 и

вывод 4 DD4, имеет большую емкость

относительно корпуса. Учитывая, что

в высокочастотных схемах фольга со

стороны установки деталей не

удаляется, выходной сигнал с DD3 при

большой скважности может "потеряться".

Поглощающий

счетчик с самозагрузкой данных

выполнен на микросхемах DD3 и DD4.

Выходной код подается на входы

записи данных. Остановимся

подробнее на записи кода. Для

работы ФАПЧ необходимо, чтобы

выходная частота счетчика была

равна опорной, т.е. 500 кГц. Для этого

входную частоту счетчика

необходимо поделить на

определенное число. В нашем случае

45:0,5 = 90 МГц.

Далее

десятичное число переводят в

двоичный эквивалент одним из

известных способов.

Полученный

код подается на входы записи данных

счетчика (вывод 15 DD3 — младший

разряд).

На

схеме опорного генератора 45 МГц

видно, что поданный код отличается

от расчетного. Реально—это число 89.

Тем не менее, схема выдает

требуемую частоту. Связано это с

тем, что изменением напряжения

питания микросхемы DD3 в пределах 4,6...5,0

В можно также регулировать

коэффициент деления . Несмотря на

кажущееся "кустарное" решение

проблемы, схема работает устойчиво.

Схема

фазового детектора и его выходных

цепей стандартная, и особенностей

не имеет.

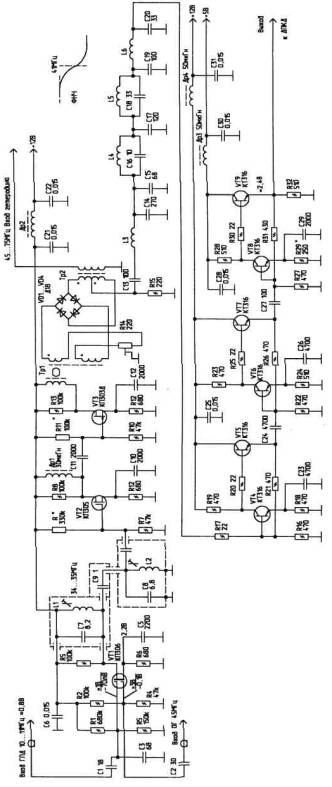

Первый

процессорный смеситель

синтезатора (рис.5) собран на

двухзатворном

Рис.5

полевом

транзисторе VT1. Режим его работы

определяется резистивными

делителями напряжения в цепях

затворов, а также емкостными

делителями поступающих на его

входы сигналов.

Нагрузкой

ПС1 является двухконтурный

полосовой фильтр L1-C7-C9-L2-C8,

настроенный на первую (переменную)

ПЧ синтезатора (34...35 МГц). Далее

следуют два каскада усиления на

транзисторах VT2 и VT3. Нагрузкой

последнего является

широкополосный трансформатор

второго процессорного смесителя,

выполненного по кольцевой

балансной схеме на диодах VD1...VD4(nC2).

(Продолжение

следует)